ECE-1387: CAD for Digital Circuit Synthesis and Layout

Fall 2013NEWS:

- Exercise #3 is posted (16 December)

- Exercise #2 is posted (22 November)

- A3 is posted (2 November)

- Exercise #1 is posted (1 November)

- A2 posted (11 October)

- A1

is extended and is due on class on October 11. Also for A1, for

the output pin equivalence, if there are unused output pins on a logic

block, your may use them. Meaning, your router may use two output

pins for a multi-fanout net, if you find it helps routability. Be

sure, however, you do not have two signals routed on the SAME output

pin (i.e. no signal shorts on output pins!). (1 October)

- Assignment #1 is posted (19 Sept)

- Info about the course paper added.

- The 2013 session of ECE1387 will include an emphasis on high-level synthesis (from C to circuits).

- Course webpage established (28 August)

Basic Information

Instructor: Jason Anderson

E-mail: janders@eecg.toronto.edu

Web: http://www.eecg.toronto.edu/~janders

Tel: 416-946-7285

Office: EA 314 (Engineering Annex)

Instructor's Office hours: Email or phone for an appointment (or drop by my office)

Lectures: Fridays from 5-7 PM, commencing on September 13, 2012

Room: BA4164 (Bahen Building)

E-mail: janders@eecg.toronto.edu

Web: http://www.eecg.toronto.edu/~janders

Tel: 416-946-7285

Office: EA 314 (Engineering Annex)

Instructor's Office hours: Email or phone for an appointment (or drop by my office)

Lectures: Fridays from 5-7 PM, commencing on September 13, 2012

Room: BA4164 (Bahen Building)

Overview

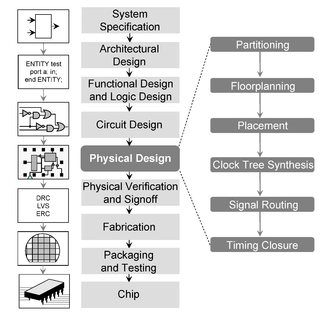

The course covers the approaches and algorithms for

automatic circuit synthesis. Topics covered will include: technology mapping,

partitioning, placement, routing, timing analysis, and high-level

synthesis. The course will include experience with existing CAD tools

and building new tools in C/C++. We will pay special attention to

synthesis issues as applied to Field-Programmable Gate Arrays (FPGAs).

Who should take this course?

The course will interest (at least) three types of

students:

1) Students whose research falls in the area of computer-aided design for FPGAs or ASICs, or whose research pertains to the architecture of such chips.

2) Digital IC design engineers: it is important to know how the tools you use work!

3) Anyone interested in seeing some real/practical applications of combinatorial optimization algorithms.

1) Students whose research falls in the area of computer-aided design for FPGAs or ASICs, or whose research pertains to the architecture of such chips.

2) Digital IC design engineers: it is important to know how the tools you use work!

3) Anyone interested in seeing some real/practical applications of combinatorial optimization algorithms.

Course Syllabus and Lecture Schedule

Readings

Information on the Course Paper

Graphics Package (Courtesy of V. Betz)

Another Graphics Package -- more "modern"

(Courtesy of Sandeep Chatterjee, chatte45@eecg.toronto.edu)

Assignments

Assignment #1: routing with pin equivalence (PDF) (circuits)Assignment #2: analytical placement, net models, power (PDF) (circuits) (solver quick start (PDF) -- no need to compile solver with BLAS)

Sample plots from Nazanin Calagar's 2012 AP implementation

C implementation of the Hungarian method (minimum-cost bibpartitate matching)

C implementation of the Hungarian method (minimum-cost bibpartitate matching)

Assignment #3: B&B partitioning (PDF) (circuits)

Exercises

Exercise #1: simulated annealing placement and negotiated congestion routing (PDF) (circuits + arch file) Paper about the VTR project (PDF)Exercise #2: multi-level partitioning with hMetis (PDF) linux binary (circuits + manual)

The linux binary is tested to work on both EECG and ECF machines.

Exercise #3: LegUp high-level synthesis. Visit this website and follow the instructions to use LegUp 3.0 on a virtual machine (called VirtualBox): http://legup.eecg.utoronto.ca/getstarted.php

My apologies for the large file size of the VM image, however, it is MUCH easier to install and use LegUp this way, versus compiling it yourself (as it needs several libraries, Altera Quartus, ModelSim, etc.) Note that the main LegUp webpage is: http://www.legup.org

The exercise is based on a tutorial we delivered at the 2013 ACM Int'l Symposium on FPGAs earlier this year: (PDF) (divide.tar.gz)